上季台積電法說會中,董事長魏哲家除釋出CoWoS產能嚴重吃緊的消息外,還提到正加速扇出型面板級封裝(FOPLP)的進行,預期3年可望展現成果;因此FOPLP也被市場視為繼CoWoS之後,最被期待的先進封裝應用。

由於FOPLP具有降低成本的優勢,也可與CoWoS併用,因此被市場視為繼CoWoS之後,最被期待的先進封裝應用。

為衝刺先進封裝產能,台積電已於8月中旬買下群創南科四廠,內部廠區代號「AP8」。由於台積電整合扇出(InFO)封裝同時包含CoWoS與FOPLP、FOWLP(扇出型晶圓級封裝)等技術,因此,AP8廠後續產能計畫也備受市場關注。

據市場研究機構Yole Developpement發布報告指出,2022年全球整合扇出型(InFo)封裝市場規模為18.6億美元,預估2026年將成長至34.3億美元,主要應用為移動裝置、消費性電子、電信和基礎設施等;其中FOWLP估為87%、FOPLP為13%。

均豪董事長陳政興表示,CoWoS產能2024年、2025年將倍增,預期2026年達到供需平衡,以及FOPLP技術約3年後會成熟,看好FOPLP有望成為下個接棒的關鍵技術

●台積電曾使用的FOWLP技術是什麼?

FOWLP技術最早是由英特爾(Intel)於2009~2010年間提出。其技術原理簡單來說,就是採用拉線的方式,將多種不同裸晶,做成像WLP製程一般埋進去,因不須使用載板材料,等於少一層封裝步驟,因此可節省近30%封裝成本;如果裸晶顆數愈多,節省的封裝層數就愈多、成本下降就愈顯著。

另,FOWLP的設計難度也低於矽穿孔(Through Silicon Via;TSV)3D IC,且接近2.5D IC概念,且封裝厚度也更加輕薄,因此採用FOWLP有助於提升晶片商產品競爭力。

但後來,圓形的FOWLP,使用上的經濟效益不如FOPLP,因此被取代。

●扇出型面板級封裝(FOPLP)技術是什麼?贏FOWLP在哪?

FOPLP之所以在近年崛起,備受關注的原因,第一個原因是,它與CoWoS可以並存,用來提升晶片效能同時降低生產成本,維持摩爾定律。

FOPLP備受矚目的第二大優勢?簡單來說就是「以方代圓」;至於CoWoS則是「搭橋」技術,優化晶片彼此連結、堆疊的技術。

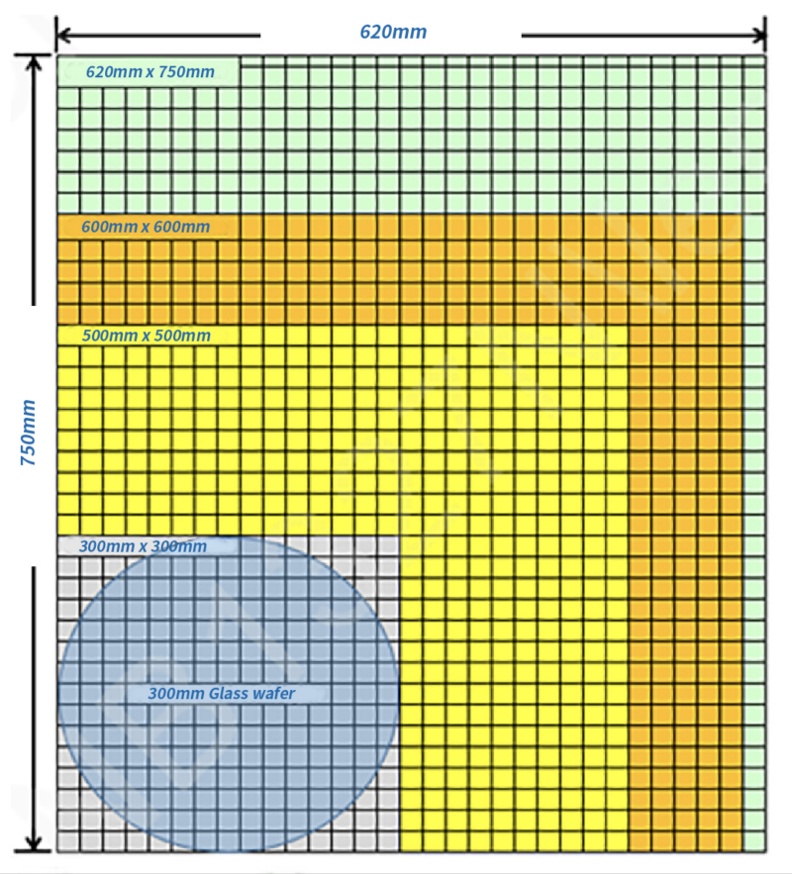

可參考以下的圖片,原本晶片生產在使用FOWLP封裝技術時,是透過切割圓形的晶圓而成,受限於形狀的關係,因此利用率無法達到最高,而FOPLP則是與面板一樣,透過「方形」基板進行堆疊(請見下圖),所以可以充分使用。

上圖是群創所提出,將現有3.5代產線活化,目前業界最大尺寸FOPLP技術:620mm X 750mm、玻璃基板(Glass Panel)、開發線寬介於 2μm ~10μm的中高階半導體封裝;其可用面積是傳統300mm Glass Wafer的7倍。未來將致力於「容納更多的I/O 數」、「體積更小」、「降低能耗」等發展方向。

FOPLP與FOWLP有何不同?

FOPLP與FOWLP(Fan-Out Wafer Level Packaging,扇出型晶圓級封裝)最大差異點在於Panelization階段所採用的載具,前者採用矩形載具/板,而後者則以圓形矽晶圓為主。

國內法人表示,扇形封裝由wafer level(晶圓級)轉換到 panel level(面板級)更具有經濟效益,而且台積電在技術論壇曾提及,FOPLP將開發用於大尺寸晶片的解決方案,而非現在FOPLP主要使用的PMIC等小尺寸晶片,提升效益更大。若以600*600(mm2)矩形載具為例,其可用面積就比12吋晶圓大逾5倍,平均載具利用率也將從57%顯著提升至87%。

●台積電的InFO_PoP與InFO_oS有何不同?

台積電則是在2012年開始投入扇出型晶圓級(FOWLP)封裝,提出了集成扇出型(Integrated Fan-Out, InFO)封裝技術,並率先用於iPhone 7系列的A10應用處理器封裝上,2016年開始量產。

目前整合扇出(InFO)、基板上晶圓上晶片封裝(CoWoS,Chip-on-Wafer-on-Substrate)以及系統整合單晶片(SoIC)都是台積電晶圓級系統整合技術(WLSI)平台的成員。而台積電目前將InFO平台,區分為InFO_PoP與InFO_oS,以下是兩者的說明。

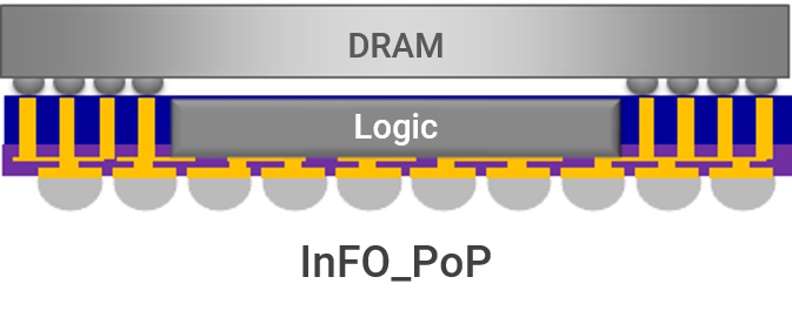

台積電InFO_PoP(請見上圖)是業界第一個3D晶圓級扇出封裝技術,具有高密度RDL(Re─Distribution Layer,重佈線層)和TIV(Through InFO Via),其將行動AP與DRAM封裝堆疊整合。與FC_PoP相比,InFO_PoP由於沒有有機基板和C4凸塊,因此具有更薄的外形和更好的電氣和熱性能。

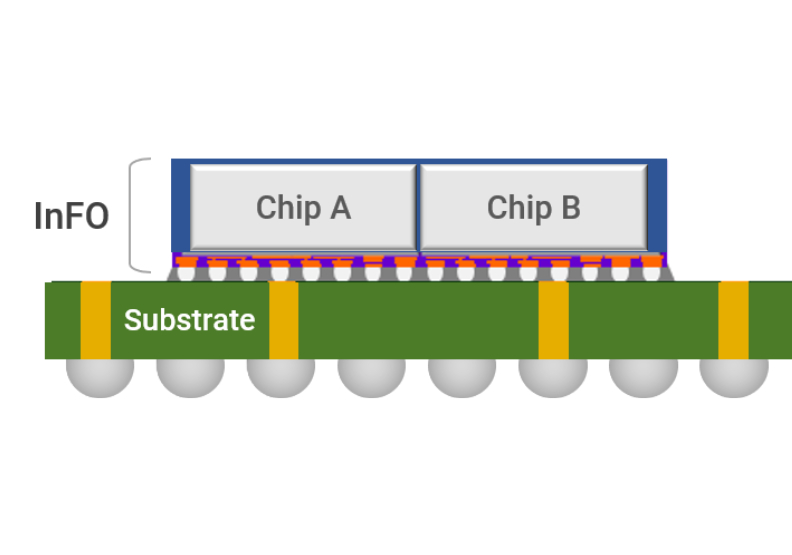

InFO_oS(請見下圖)則是利用InFO技術整合多個先進邏輯晶片,具有更高密度的 2/2μm RDL 線寬/間距,常用於5G網路應用上。它可在SoC上實現混合焊盤間距,在 >65 x 65mm 基板上具有最小 40μm I/O 間距、最小 130μm C4 Cu 凸塊間距和 > 2 倍掩模版尺寸 InFO。台積電InFO_oS的產量自2017年第4季大幅增加,且隨客戶繼續加速在下一代產品中採用小晶片封裝方案,預計將整合更多晶片。

●台積電InFO發展史

台積電發展InFO(整合扇出)已有十多年的歷史,也是最早量產的先進封裝技術。台積電InFO是一個創新的晶圓級系統整合技術平台,具有高密度RDL(重新分佈層)和TIV(絕緣體通孔,Through InFO Via),可實現行動、高效能運算等各種應用的高密度互連和效能。台積電InFO平台可提供針對特定應用進行最佳化的各種2D和3D封裝方案。

| 時間 | 事件 |

|---|---|

| 2012年 | 《IEDM 2012》發表:高性能整合扇出晶圓級封裝 (InFO─WLP):技術與系統集成 |

| 2013年 |

|

| 2015年 |

|

| 2016年 |

|

| 2017年 |

|

| 2018年 |

|

| 2019年 |

|

| 2020年 |

|

| 2021年 |

|

| 資料來源:台積電官網 製表:魏鑫陽 | |

●FOPLP概念股有哪些?

從2017起,除台積電外,各家半導體廠都有投入扇出型封裝,但至目前為止,除台積電,其他廠商都未有明顯的營收貢獻。不過傳出輝達(NVIDIA)最快2026年導入面板級扇出型封裝(FOPLP)後,且InFO與CoWoS先進封裝各有其應用領域、兩者互不相斥,所以法人仍看好AI浪潮將持續推升先進封裝需求。

其中,群創自2017年投入FOPLP研發,日月光與大廠研發CPU、電源IC等FOPLP技術,東捷則有FOPLP相關切割機,友威科水平式電漿轉刻設備,鑫科特殊合金載板等等,相關FOPLP概念股請看下表所示。

| 分類 | 廠商 |

|---|---|

| 晶圓製造 | 台積電(2330) |

| IC封測 | 日月光(3711)、力成(6239)、超峰(2441)、京元電(2449)、欣銓(3264)、頎邦(6147)、矽格(6257) |

| FOPLP技術 | 群創(3481) |

| 設備廠 | 友威科(3580)、東捷(8064)、鑫科(3663)、弘塑(3131)、辛耘(3583)、志聖(2467)、均豪(5443) |

| 資料整理:魏鑫陽 | |