GB200年底出貨在即,輝達(NVIDIA)持續追加台積電CoWoS訂單,激勵近期CoWoS概念股表現強勢。到底什麼是CoWoS?台積電的CoWoS-R、CoWoS-L又什麼差別呢?

輝達(NVIDIA)AI伺服器GB200專用晶片Blackwell GPU,採用台積電CoWoS先進封裝技術,為此,輝達不僅持續追加台積電CoWoS訂單,預計11月開始量產出貨。外資法人指出,輝達GB200伺服器第一階段出貨將落在今年底,相關供應鏈包括晶片代工廠台積電,運算主板的鴻海、緯創等,激勵近期CoWoS概念股表現強勢。

日前輝達執行長黃仁勳接受美國媒體CNBC專訪時透露:「市場對Blackwell需求很瘋狂(insane)。」由於生成式AI帶動高速運算需求,造成台積電產能CoWoS供不應求,本土法人預期,2024年底台積電CoWoS的總產能相較2023年將提升超過150%,而隨著台積電加大、加速CoWoS產能擴充力道,輝達GB200伺服器出貨可望在2025年逐步放量,且CoWoS對於台積電營收、獲利的助益日益增加。

● CoWoS是什麼?

CoWoS就是使用2.5D/3D的晶片堆疊技術,將不同功能的晶片整合封裝至基板上。但若要用簡單白話來解釋,CoWos技術和傳統晶片製作方式有何不同,或可類比為搭橋。因為以前晶片只需要實現單一功能,但是現在AI,需要更多功能的晶片連結在一起才有辦法成功運作。這些晶片就像孤島,需要連結起來,CoWos就是連結起這諸多晶片的橋梁。

也因此,CoWos搭橋起來後,優勢不只是在於節省空間、還能降低功耗、提高晶片效能,同時達到加速運算但成本仍可控的目標。目前已廣泛應用於高效能運算、AI晶片等領域上。

其實CoWoS(Chip-on-Wafer-on-Substrate)與SoIC一樣,都屬於先進封裝技術的一種。而所謂的先進封裝技術,就是隨晶片線路愈做愈細小,單一晶片電晶體密度逐漸逼近極限,為了延續摩爾定律,所發展出的多種封裝方法。

依據研調機構Yole預估,全球先進封裝市場規模將由2022年時的443億美元,2028年將成長至786億美元、年複合成長率為10.6%。

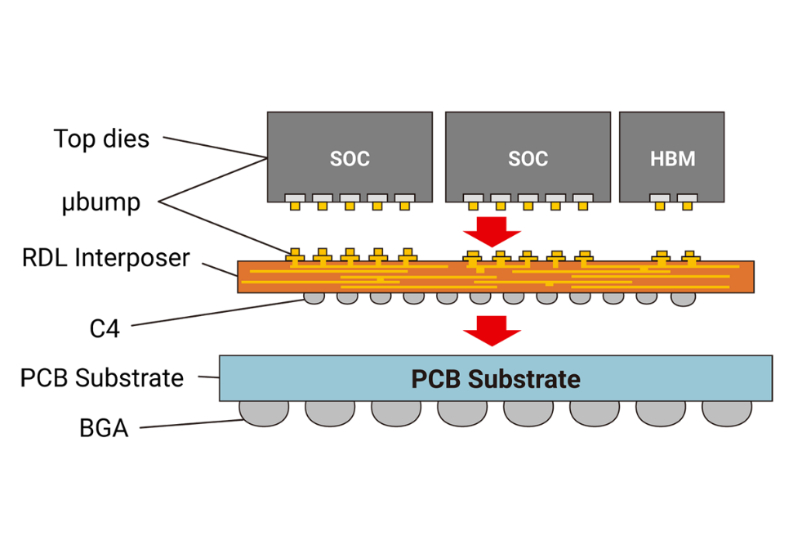

進一步解釋,我們則可將CoWoS這字拆開,分成CoW(Chip-on-Wafer)以及WoS(Wafer-on-Substrate)兩大部分。請見下圖:

◼ CoW(Chip-on-Wafer):將晶片堆疊在導線載板上。

- ◼ WoS(Wafer-on-Substrate):晶片堆疊在基板上,或將晶片堆疊後封裝於基板上。而根據排列形式,CoWoS可分為2.5D與3D不同型態。

當然,CoWoS的技術門檻也相當高,除了晶片之間的堆疊和連接考驗晶圓廠對精細度的掌握,另,多個晶片堆疊後對於散熱技術的要求也急遽增加。

● 關於台積電CoWoS平台

針於先進封裝技術,台積電構建了晶圓級系統整合技術(WLSI)平台,先後推出整合型扇出(InFO)、基板上晶圓上晶片封裝以及系統整合單晶片(SoIC)等。也就是說,台積電具有將上述三種技術整合於同一晶片上的能力。

台積電的CoWoS平台,為高效能運算應用提供同類最佳的效能和最高的整合密度。此晶圓級系統整合平台提供多種中介層尺寸、HBM立方體數量和封裝尺寸。它可以實現大於2倍標線尺寸(或約1700mm 2)的中介層,領先將SoC晶片與四個以上的HBM2/HBM2E立方體整合在一起。

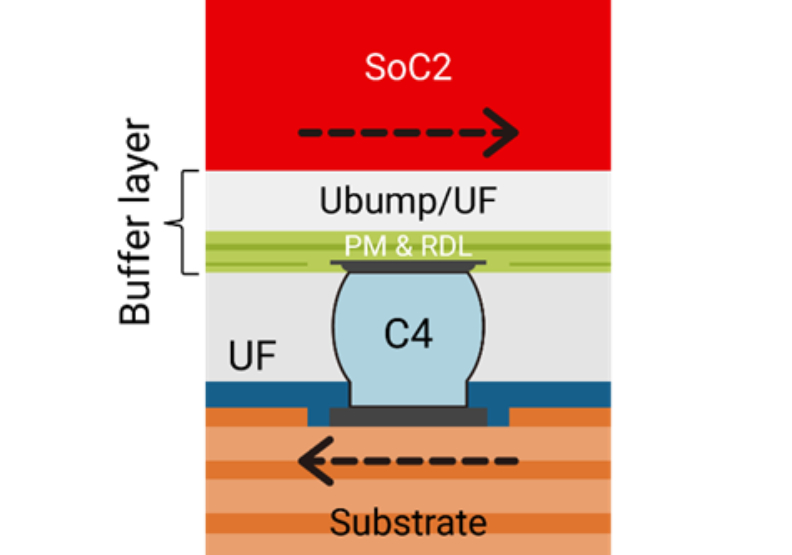

◎ CoWoS-R是什麼?

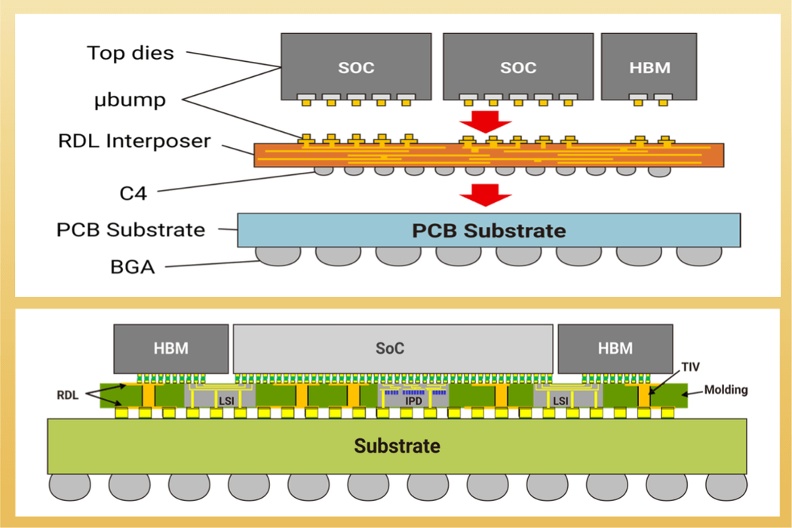

CoWoS-R是台積電CoWoS先進封裝系列的成員之一。CoWoS-R利用InFO技術,透過RDL中介層並服務於小晶片之間的互連,特別是在HBM(高頻寬記憶體)和SoC異質整合中。其中,RDL中介層由聚合物和銅跡線組成,具有相對機械柔性;這種柔性靈活性增強了 C4 接頭的完整性,並允許新封裝擴大其尺寸以滿足更複雜的功能需求。請見下圖:

◎ CoWoS-R的優點

CoWoS-R技術的主要特點包括(請見下圖):

1. RDL中介層:最多可由6L銅層組成,且最小佈線可達4um間距(2um線寬/間距)。

2. RDL互連:可提供良好的訊號和電源完整性效能,並具有較低的路由線 RC 值,以實現高傳輸資料速率。共面 GSGSG 和具有六個 RDL 互連的層間接地屏蔽可提供卓越的電氣性能。

3. RDL層和C4/UF層提供了良好的緩衝效果,讓C4的應變能密度大大降低。

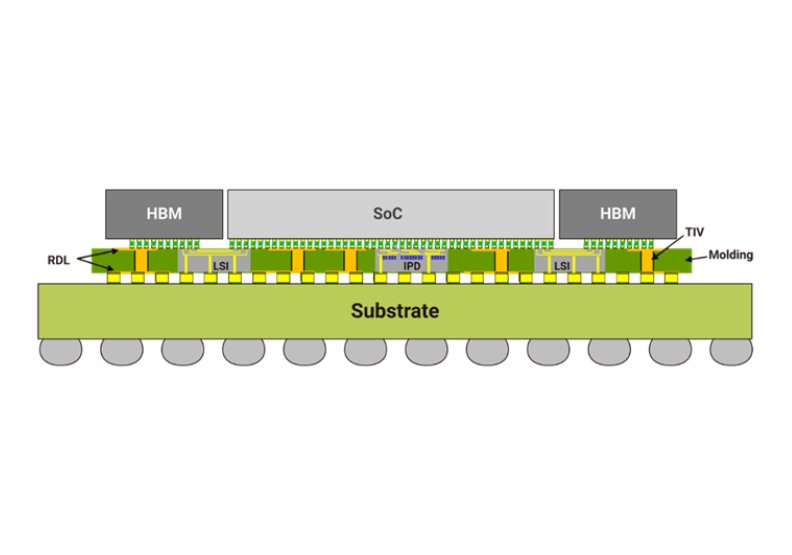

◎ CoWoS-L是什麼?

CoWoS-L是CoWoS平台中的晶片封裝方式之一。它結合了CoWoS-S和InFO技術的優點,使用中介層與LSI(本地矽互連)晶片提供最靈活的集成,用於晶片到晶片的整合。該產品從具有 1x SoC + 4x HBM 立方體的 1.5X 標線中介層尺寸開始,並將繼續擴大尺寸以整合更多晶片。請見下圖所示:

◎ CoWoS-L的優點

CoWoS-L的主要特點包括:

1. LSI晶片,透過多層亞微米銅線實現高佈線密度晶片間互連。LSI晶片在每個產品中可以具有多種連接架構(例如SoC到SoC、SoC到chiplet、SoC到HBM…等),並且還可以在多個產品中重複使用。

2. 基於模塑的中介層,在正面和背面均具有寬間距的RDL層,以及用於訊號和電力傳輸的 TIV(穿插器通孔),可在高速傳輸中提供低損耗的高頻訊號。

3. 能夠在SoC晶片正下方整合其他元件,例如獨立的IPD(整合式被動元件),以支援其具有更好的 PI/SI 的訊號通訊。

● CoWoS的發展沿革

你可能不知道「先進封裝」、「CoWoS」等字詞,都是出自於鴻海集團半導體策略長蔣尚義當年還在台積電任職之時。蔣尚義曾透露,約2009年前後,發現摩爾定律逐漸失效,封裝技術反倒變成瓶頸時,為了解決這個問題,後來逐漸展開枝展葉,發展出今日的CoWoS、InFO等技術。

| 時間 | 事件 |

| 2011年 | 《ECTE 2011》發表:適用於28奈米技術FPGA的TSV內插器和互連的高級可靠性研究 |

| 2012年 |

|

| 2013年 |

|

| 2014年 |

|

| 2015年 |

|

| 2016年 |

|

| 2017年 |

|

| 2018年 |

|

| 2019年 |

|

| 2020年 |

|

| 2021年 |

|

| 2022年 |

|

| 2023年 |

|

| 2024年 |

|

| 資料來源:台積電官網 | |

● CoWoS與SoIC有何不同?

CoWoS、SoIC同屬先進封裝的成員,也同樣是台積電晶圓級系統整合技術(WLSI)平台上。與CoWoS著重於中介層的堆疊方式不同,SoIC則是去除了矽仲介版(Interposer),通過矽穿孔(TSV)或是金屬層直接將不同功能的晶片連接在一起。兩者都是為了提高晶片效率、減少能耗、維持摩爾定律等目的。

台積電已歸納先進封裝隸屬3D Fabric系統整合平台當中,包含三大部分:3D矽堆疊技術的SoIC系列,以及後段的先進封裝CoWoS家族、InFo家族。

● CoWoS概念股有哪些?

去年生成式AI橫空出世,隨各大廠紛紛擴增AI算力、AI伺服器的同時,對於晶片效能、體積、散熱、成本及封裝等要求更嚴苛,這也讓CoWoS先進封裝大放異彩,成為市場追捧的主流技術,其中台積電更是備受全球關注。那麼CoWoS概念股又有那些呢?以下挑選台廠中具有CoWoS技術,以及相關測試、載板、產線製程的CoWoS概念股名單。

| 類別 | 廠商 |

| CoWoS封裝與測試 | 台積電(2330)、日月光(3711)、京元電(2449) |

| HDI載板與基板 | 欣興(3037)、楠梓電(2316) |

| 測試版卡與製程設備 | 精測(6510)、均豪(5443)、萬潤(6187)、辛耘(3583)、弘塑(3131)、均華(6640)、志聖(2467)、穎威(6515)、旺矽(6223) |

| 資料整理:魏鑫陽 | |

● 台積電CoWoS的發展現況?

今年6月台積電嘉義先進封測AP七廠的一期P1廠(原定為CoWoS產線),因發現遺跡而短暫停工,目前行政單位確定今年10月會清理完畢、並移交給台積電,法人評估,將不影響原本預估的裝機時程。

另,法人圈也傳出,因台積電購入群創南科廠將作為先進封測AP八廠,因不需環評且土建廠房均已完成,因此建線進度可望超前1年以上,AP八廠產能可望提前至2025年第4季完成,而CoWoS 2025年月產能也將從原本的6~7萬片,再度上修至近8萬片。

研調公司IDC也表示,輝達需要台積電已規劃的CoWoS一半產能,方能應付AI晶片訂單,但台積電CoWoS產能目前僅完成三分之一。此外,超微(AMD)、博通等AI大廠也正排隊等候台積電CoWoS產能中。