美國2025川普上任後,預計擴大對中國管制半導體製程兩大基石:EDA與EUA,加強限制其發展7奈米以下製程。對相關的台灣半導體業者有沾光效應嗎?台積電(2330)可能繼續成就「一個人的武林」或有衝擊?到底EDA與EUA是什麼,而High-NA EUV對於埃米製程乃至於超摩爾定律有何重要性?本文終極拆解。

半導體產業中,技術進步與創新是推動行業向前發展的核心力量。隨著製程技術逐漸邁入7nm、5nm甚至更先進的節點,晶片設計與製造的複雜性持續提升;這樣的背景下,兩項關鍵技術—EDA(Electronic Design Automation,電子設計自動化)與EUA(Extreme Ultraviolet Adoption,極紫外光機)—成為半導體製程基石,特別是High-NA EUV(高數值孔徑極紫外光機台)的出現,更為突破物理極限提供了嶄新的可能性。

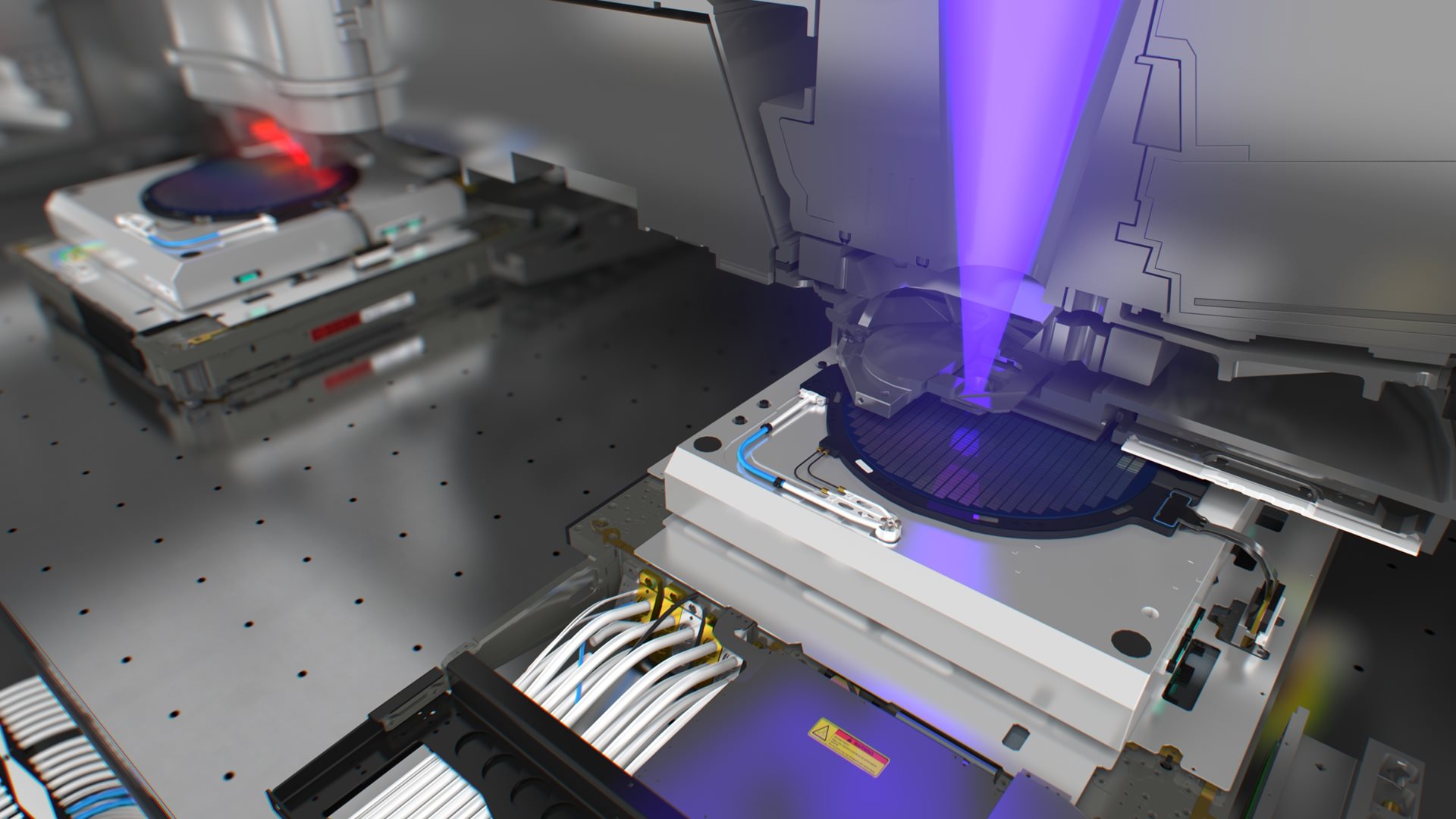

ASML作為全球唯一的EUV機台供應商,其技術創新和市場供應的核心地位不可撼動。台積電、三星與英特爾等產業龍頭的技術競爭,也持續推動 EUV 和 High-NA EUV 的發展。本文將深入探討EDA與EUA的定義、應用場景及其在半導體產業中的重要性,並進一步剖析EUA到High-NA EUV的技術演進與未來展望,同時分析美國對EDA和EUA技術出口禁令的影響。

EDA是什麼?

EDA(Electronic Design Automation,電子設計自動化)是一套專為晶片設計而開發的軟體工具。EDA 的出現與發展,讓設計師能夠以高效且精確的方式完成從晶片架構設計到製造準備的全過程。

EDA的四大核心功能:

• 晶片設計:提供自動化工具,協助設計師完成邏輯電路的設計、佈局與模擬。

• 驗證:確保設計符合規格,包括功能驗證、時序驗證與邏輯驗證。

• 佈局與布線:自動化完成元件的物理佈局與連線設計,確保性能最優化。

• 製造準備:生成設計檔案(如 GDSII 格式),準備送往晶圓代工廠進行製造。

EDA的主要工具與廠商:

• Synopsys:提供全面的晶片設計與驗證解決方案。

• Cadence:專注於電路設計、模擬與封裝技術。

• Mentor Graphics(現為 Siemens EDA):提供 PCB 設計與驗證工具。

EDA的強大能力,使得工程師可以高效應對晶片設計日益增長的複雜性,並確保IC設計成果能夠順利進入製造環節。

EUA是什麼?

EUA(Extreme Ultraviolet Adoption)是指極紫外光(EUV)技術在半導體製造中的應用與普及。EUV是目前最先進的光刻技術,利用波長僅13.5nm的極紫外光,能實現更高的解析度,滿足先進製程對微縮技術的需求。

EUV的技術優勢

• 更高解析度:相比於傳統的深紫外光(DUV,193nm),EUV能支援更小的特徵尺寸,減少多重曝光的需求。

• 簡化製程:EUV可在單次曝光中完成更精細的圖案,降低製造複雜性。

• 提升性能與良率:EUV支援更密集的元件設計,提高晶片性能並減少缺陷率。

EUV的挑戰

- • 高成本:EUV光刻機台價格高昂(每台約1.5億至3億美元)。

- • 技術門檻:包括光源強度、光罩設計與抗蝕劑材料的開發。

- • 基礎設施需求:EUV光刻對無塵室的潔淨度與穩定性要求極高。

目前,ASML是全球唯一能生產EUV機台的公司,台積電、三星與Intel等晶圓代工廠已廣泛採用EUV技術,推動7nm、5nm節點的量產。

EDA與EUA在半導體產業中的重要性

EDA與EUA雖然應用於半導體製程的不同階段,但兩者在半導體產業中密切相關,形成設計與製造的完整生態系統。以下簡單說明。

1. 設計與製造的銜接

- • EDA的角色:設計師利用EDA工具完成晶片設計,生成適合EUV製程的設計檔案。

- • EUA的角色:製造廠利用EUV光刻技術將設計轉化為晶圓上的物理結構。

EDA的輸出必須滿足 EUV 製程的技術需求,確保設計能被正確地轉化為晶圓上的圖案。

2.支援先進製程需求

隨半導體製程進入3nm以下節點,晶片設計複雜性增加,對EDA工具要求更高:

- • 更精準的模擬:考慮EUV曝光模糊與光罩效應。

- • 更高密度設計:滿足EUV支持的小特徵尺寸需求。

- • DFM(Design for Manufacturing):幫助設計師優化設計,以適應EUV製程的限制。

3.光罩設計與驗證

EUV技術依賴高精度光罩,而EDA工具能協助完成光罩設計與光學模擬,確保最終成品符合設計規範。EDA與EUA兩者的協同合作,確保了IC設計與晶圓製造的高效整合,持續推動半導體技術的進步。

EUA到High-NA EUV的技術演進

High-NA EUV(高數值孔徑極紫外光機台)是EUV技術的升級版本,旨在進一步提高光刻解析度,支持2nm和以下節點,也就是應用於高性能運算(HPC)、人工智慧(AI)加速器與高端處理器的晶片設計,更是跨入埃米時代的關鍵之一。

High-NA EUV的特點與優勢

- • 數值孔徑提升:傳統EUV機台的數值孔徑(NA)為0.33;而High-NA EUV將數值孔徑提高到0.55,解析度大幅提升。

- • 更高精度:支援更細小的圖案,減少多重曝光需求;同時改善線邊粗糙度(Line Edge Roughness, LER)。

ASML的重要性與全球影響力

ASML是全球唯一能提供EUV和High-NAEUV機台的廠商,其技術和產品對半導體產業具有決定性影響。

- • 技術領先地位:ASML投入數十年的研發,率先突破EUV光刻技術的多項關鍵挑戰,包括光源穩定性和高數值孔徑的光學設計。而High-NA EUV的推出,更鞏固了其市場壟斷地位。

- • 全球供應鏈依賴:台積電、三星和英特爾等主要晶圓代工廠高度依賴ASML的EUV機台,以實現先進製程的量產。也可說,ASML的產品供應直接影響全球半導體技術的發展速度。

- • 地緣政治影響:由於EUV技術的戰略重要性,ASML也成為國際科技競爭的焦點,例如限制中國購買EUV機台的出口管制。

摩爾定律與半導體產業的挑戰

摩爾定律預測電晶體密度每兩年翻倍,但隨著製程技術接近物理極限,使得技術推進變得困難。雖然摩爾定律雖然面臨挑戰,但技術創新仍在不斷推動半導體產業,特別是新進封裝、創新材料的出現,讓摩爾定律得以延續。

摩爾技術的挑戰:

• 量子效應:晶體管尺寸縮小至數奈米級別後,電子洩漏和量子隧穿效應對性能造成限制。

• 成本上升:每一代製程技術的開發與量產成本呈指數增長。

- 製程解決方案:

- • EUV和High-NAEUV:通過提升解析度支持更小的特徵尺寸。

- • 3D堆疊技術:如台積電的CoWoS和三星的X-Cube,透過垂直整合提升晶片性能。

- • 新材料與架構:採用GAA(Gate-All-Around)晶體管結構和2D材料(如石墨烯)。

美國對中國的EDA禁令與影響

EDA(電子設計自動化)技術是晶片設計的核心工具,美國對中國的EDA出口管制對半導體產業更產生了深遠影響。

1.限制的內容

- • 禁止向中國出口支持先進製程(如7nm及以下)的EDA軟體。

- • 主要影響廠商:Synopsys、Cadence和Siemens EDA。

2.對中國的影響

- • 設計能力受限:中國晶片設計公司難以進行高階晶片的設計,對7nm以下製程的開發造成瓶頸。

- • 技術追趕放緩:由於EDA是晶片設計流程的基石,缺乏這些工具將大幅減緩中國追趕先進技術的速度。

3.中國的應對措施

- • 加速自研EDA工具:例如華大九天等中國本土廠商正在努力縮小與國際大廠的技術差距。

- • 尋求替代方案:與其他非美國技術來源合作,開發替代性的設計工具。

4.全球供應鏈的影響

- • 技術生態分裂:出口管制可能加速全球半導體生態的區域化和分裂。

- • 研發成本上升:國際企業需應對潛在的市場減少和研發投入增加的挑戰。

美國對中國的EUA禁令與影響

EUA(極紫外光採用)技術是支持先進製程的關鍵技術,美國及其盟友對中國的EUA出口限制集中在EUV光刻機台及相關技術。ASML執行長富凱(Christophe Fouquet)就曾表示,由於無法獲得先進的EUV曝光機,中國的晶片技術可能會落後西方10至15年。

1.限制內容

- • 禁止ASML向中國出口EUV光刻機台,特別是用於7nm以下製程的設備。

- • 禁止出口與EUV相關的核心技術,包括光源系統與光罩設計工具。

2.對中國的影響

- • 製造能力受限:缺乏EUV機台下,中國晶圓代工廠難以突破7nm製程瓶頸。

- • 技術自研挑戰:開發EUV技術需要數十年投入和龐大的資金支持,中國短期內難以實現。

3.中國的應對措施

- • 加強DUV技術開發:聚焦在成熟製程的提升,延長DUV技術的生命週期。

- • 探索替代技術:嘗試透過多重曝光技術實現接近EUV的解析度,或研究其他光刻方法。

4. 全球供應鏈的影響

- • 市場份額重分配:中國無法參與高階製程競爭,台積電和三星等企業在先進製程中的領先地位將進一步鞏固。

- • 技術分裂風險:出口限制可能導致中國發展與全球不同的技術路徑,增加全球半導體市場的不確定性。

美國禁令對ASML、三大EDA與台灣業者的影響

美國對中國的EDA和EUA出口禁令,對ASML與三大EDA業者產生巨大的影響,至於台灣半導體業者,影響則可分為正面與負面。以下分別說明:

1.對ASML的影響

- • 營收短期受限:由於中國是全球半導體設備的重要市場之一,禁止出口EUV機台可能對ASML的部分營收構成壓力。

- • 技術優勢未受動搖:儘管無法出口至中國,ASML在先進光刻技術上的壟斷地位仍然穩固,來自台積電、三星和英特爾的需求將持續增長。

- • 市場多元化策略:ASML正積極拓展歐美及其他市場,彌補中國市場的限制。

2.對三大EDA業者的影響

- • 銷售縮減:中國市場對Synopsys、Cadence和Siemens EDA的銷售將受到直接影響。

- • 技術需求轉移:全球半導體廠商可能加大對EDA工具的依賴,尤其是在應對更複雜製程需求方面,推動這些公司進一步創新。

- • 地緣政治壓力:三大EDA業者需平衡商業利益與政府政策的要求,可能影響其全球布局策略。

3.對台灣半導體業者的影響

A.正面影響(加分)

- • 市場份額增加:台積電作為全球領先的晶圓代工廠,在先進製程(如7nm、5nm及以下)中的優勢將進一步擴大。由於中國無法取得EUV機台和先進EDA工具,其高階製程的競爭力將大幅降低。

- • 技術領先地位鞏固:台積電得以維持其在先進製程中的領導地位,並吸引更多來自全球客戶的訂單,尤其是需要高性能運算(HPC)和AI晶片的企業。

B.負面影響(減分)

- • 市場分裂風險:中國可能轉向發展本土化的技術生態,減少對台灣半導體產品的依賴,長期可能導致市場份額流失。

- • 地緣政治風險升高:中國可能因技術限制而加大對台灣半導體供應鏈的壓力,進一步加劇地區緊張局勢。

EDA與EUA是推動半導體產業發展的兩大核心技術。EDA提供了高效的設計工具,支撐晶片設計的創新;EUA則引領光刻製程,實現更高解析度的製造能力。隨High-NA EUV的到來,半導體製程將進一步邁向物理極限。

ASML作為EUV技術的唯一供應商,持續引領行業發展,而台積電、三星與英特爾的競爭則推動了製程創新。然而,三星、英特爾在3奈米以下發展陷入瓶頸,不僅影響其全球建廠時程,也降低其對High-NA EUV的需求,衝擊ASML營收表現。

未來,面對摩爾定律的挑戰與地緣政治的不確定性,EDA工具將需進一步升級,以支持High-NA EUV帶來的更高製程需求,而中國的自主化進程亦可能改變產業的技術生態。EDA與EUA的協同作用,將為半導體技術創造更多可能性,引領行業進入全新的高度。